Contraction of the second s

# Advanced packaging and heterogeneous integration Optical metrology solutions

for next-generation semiconductors

| INTRODUCTION                          | 3  |

|---------------------------------------|----|

| More Moore vs More than Moore         | 4  |

| Applications and markets              | 6  |

| Integration strategies and challenges | 7  |

| ADVANCED PACKAGING                    | 9  |

| Through silicon vias                  | 11 |

| Microbumps                            | 12 |

| Wafer glue                            | 13 |

| Redistribution layers                 | 14 |

| FEOL and BEOL                         | 15 |

| HETEROGENEOUS INTEGRATION             | 16 |

| CPO Waveguides                        | 18 |

| Microlenses                           | 19 |

| New materials                         | 20 |

| MEMS                                  | 21 |

| PCB applications                      | 22 |

| CONCLUSIONS                           | 23 |

## SENSOFAR

## ADVANCED PACKAGING

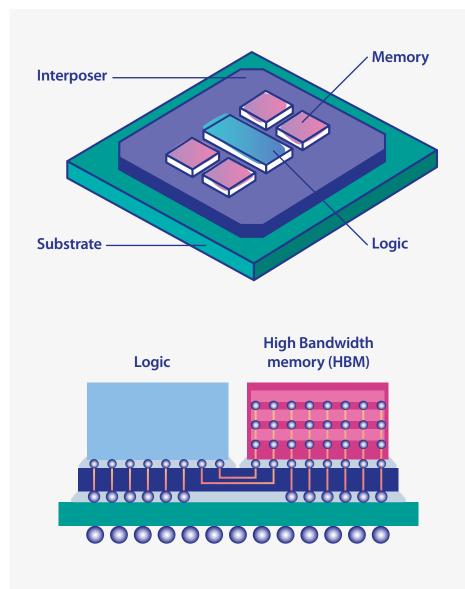

Advanced packaging techniques vary in complexity and design, each offering unique advantages for improving performance, integration density, and energy efficiency.

2.5D integration enhances connectivity by placing multiple dies side by side on a silicon or organic interposer, which serves as a high-density routing layer. This approach reduces power consumption and increases bandwidth, making it ideal for High Bandwidth Memory (HBM) integration with GPUs and Al accelerators. One of the most famous 2.5D integrations is Chip-on-Wafer-on-Substrate (CoWoS<sup>®</sup>).

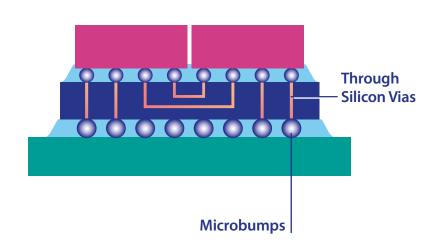

For even greater integration, 3D packaging vertically stacks multiple dies, interconnecting them through Through-Silicon Vias (TSV)—microscopic vertical channels that allow direct electrical communication between layers. This architecture significantly reduces data transfer distances, improving speed and efficiency while minimizing power loss. 3D integration is widely adopted in high-density memory solutions like 3D NAND flash and advanced processor architectures like Intel's Foveros technology.

## SENSOFAR

Micro bumps and hybrid bonding are crucial enablers of both 2.5D and 3D integration, two ways to create very high-density wafer-to-wafer or die-to-wafer interconnects.

Beyond 2.5D and 3D integration, wafer-level and panellevel packaging have emerged as key strategies for improving efficiency, yield, and scalability in advanced semiconductor manufacturing. Wafer-level packaging (WLP) processes entire wafers before singulation, enabling finer interconnect pitches and reducing package size. Fan-Out Wafer-Level Packaging (FOWLP) enhances this by expanding interconnects beyond the die footprint, improving thermal management and I/O density, making it ideal for mobile and highperformance applications. Fan-Out Panel-Level Packaging (FOPLP) further increases production efficiency by processing chips on larger rectangular panels, lowering costs and material waste, particularly in high-volume applications like automotive electronics.

These advanced packaging methods introduce significant metrology challenges, requiring precise measurements of TSV depths, microbump heights, interconnect alignment, and bonding surface roughness. High-resolution 3D optical metrology plays a critical role in ensuring process accuracy, optimizing performance, and minimizing defects in nextgeneration semiconductor packaging.

THROUGH SILICON VIAS

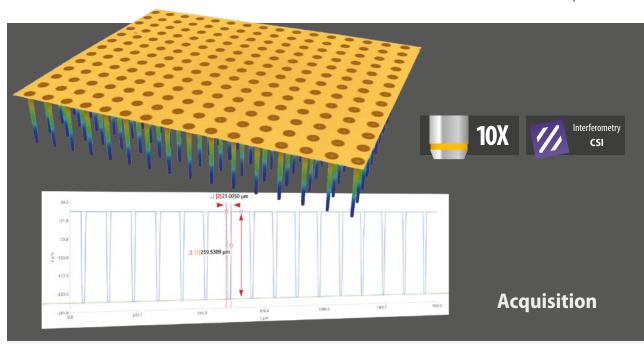

One key parameter to characterize these advanced semiconductor architectures is the depth of the interposer layer. This layer is designed to be as thin as possible to minimize the space it occupies. The challenge lies in accurately measuring through these small but deep holes, which can be measured using the S neox and Interferometry with low magnification.

#### Hole SensoPRO Plugins

### Analysis

| epth          | 55.5053 | μm |

|---------------|---------|----|

| opDiameter    | 67.1318 | μm |

| ottomDiameter | 55.6473 | μm |

| pace          | 77.9965 | μm |

| paceAvg       | 95.8276 | μm |

| perture       |         |    |

| IC            | 60.7793 | μm |

| ICC           | 73.6116 | μm |

| oundness      | 82.5676 | 96 |

| opSa          | 0.3451  | μm |

| lottomSa      | 4.9104  | μm |

| ottomSp       | 2.6141  | μm |

| ottomSv       | 3.7889  | μm |

| laxDepth      | 58.1194 | μm |

| linDepth      | 59.2942 | μm |

| epthRange     | 1.1748  | μm |

| it            | 2.6141  | μm |

| P-TD          | 0.8268  |    |

# Unlock the complete White paper by signing up to

METROLOGY